人工智能

人工智能

通过先进的测试解决方案推动人工智能领域的创新

泰瑞达是您值得信赖的合作伙伴,我们先进的自动化测试设备 (ATE) 可以帮助您的芯片快速导入量产、改进良率并提高芯片性能,进而满足新一代 AI 芯片不断增长的需求。

我们深刻了解 AI 芯片从设计到量产的制造全流程

AI芯片的发展对测试设备提出了更高要求:需要具备大电流、高性能供电能力和灵活的数字测试板卡。AI芯片设计带来了新的要求,必须提升测试覆盖率,确保生产出高质量、高良率的复杂AI芯片。

AI 芯片测试客户对泰瑞达的信赖源自于我们了解客户需要什么,以及在哪些关键的工作流程中会起到重要作用。

我们赢得了 AI 客户的信赖

泰瑞达帮助领先的创新企业部署先进的测试能力,以便快速引入新的 AI 芯片、改进良率并提高芯片的性能。

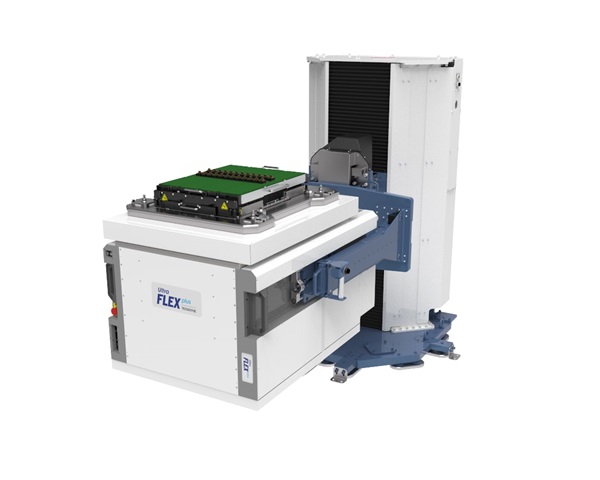

泰瑞达UltraFLEX系列测试设备助力精准高效测试

UltraFLEX 系列

用于保障 64 位中央处理器 (CPU)、TB 级磁盘驱动芯片、应用处理器 (AP)、移动电源管理芯片、安全类芯片以及其它复杂 SoC 芯片的测试质量、产能和快速上市时间。

全新的高性能第三代板卡套装

UltraPin2200 – 新一代数字板卡

- 高密度,每个板卡有512 个通道

- 每个板卡有32 个向量发生器,具有并发测试的能力,也可以为每个工位提供独立的向量测试功能

- 适用于非确定性数据测试的专用内存

- 最高达 16Gbit Scan的测试容量,采用灵活的向量存储架构

- 跨工位向量数据共享

UVS256-HP – 高密度、高灵活性的通用电源板卡

- 每个板卡有256 个通道

- 灵活的通道merge能力

- 卓越的动态性能

- 低噪声

- 可提供并测量四象限电压或电流

UVS64——新一代核心电源板卡

- 高度精确稳定,适用于芯片core 电源

- 优异的动态性能

- <1mV 的 6 sigma电压精度

- 每个板卡最高输出可达 320A

- 电源 merge后单通道最高可达 1600A

- 支持最高达 2560A的瞬时系统阶跃电流

UltraPAC300——新一代高密度模拟板卡

- 高性能音频和基带芯片测试板卡

- 覆盖300MHz 带宽

- 单通道支持高速和高分辨率两种模式

UltraSerial10G——这款高速串行板卡可测试不断发展的串行总线芯片,并模拟待测芯片工作环境,能在最短的测试时间内实现最佳测试质量和最高产能。

- 每个板卡有20对差分驱动和20对差分接收端口(40个通道/80个管脚)

- 数据速率覆盖42Mbps到10.7Gbps,具有426M向量存储空间和1G Capture存储空间

- 直流参数测量硬件

- 接收数据沿自动器对齐(CDR)以应对时序和数据不确定性

- 板卡内环回

- PRBS硬件

- Jitter Injection和Jitter/Eye测量硬件

- 所有这些功能旨在为SerDes总线提供高效的测试方法

- 支持PCIe协议测试