光速级测试:泰瑞达赋能硅光子与共封装光学可扩展测试

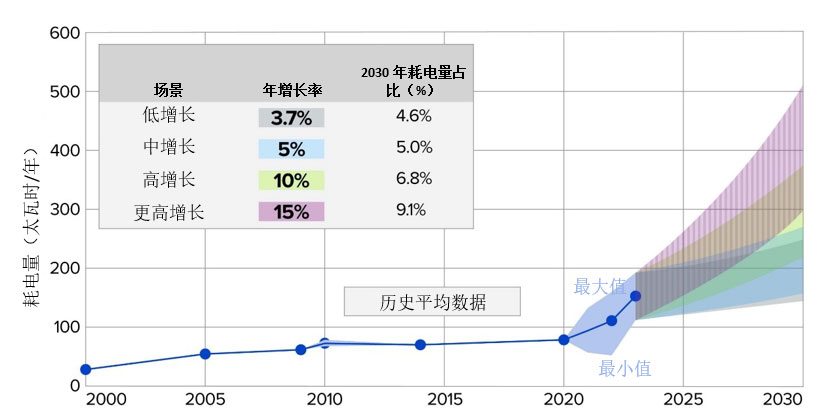

如今,单次ChatGPT查询的功耗约为传统谷歌搜索的十倍,且随着人工智能(AI)向图像和视频生成领域拓展,这一功耗还将持续攀升。不仅AI领域呈现这样的增长态势,云计算与高性能计算(HPC)领域的发展同样迅猛。据预测,到2030年,美国数据中心耗电量占全美总耗电量的比例将高达9.1%。

图1:美国数据中心潜在耗电量预测:2023年-2030年(来源:EPRI)

耗电量的激增正推动主流芯片设计厂商加大对光互连解决方案的投入,尤其是硅光子学(SiPh)与共封装光学(CPO)技术,以此实现降低能耗的目标。博通公司报告称,其首款共封装光学交换芯片实现了30%的功耗节省;而英伟达近期推出的一款CPO交换芯片,能效相比传统可插拔收发器提升了3.5倍。

硅光子学与共封装光学技术:开启互联互通新时代

硅光子学借助硅材料制备光子集成电路(PIC),这类芯片集成了光调制器、光电探测器及光波导。其采用成熟的CMOS工艺节点(65nm或以上)制造,相较于磷化铟(InP)或砷化镓(GaAs)方案,可实现更快的数据传输速率(200G以上对比不足100G)、更低的功耗及更大的带宽,非常适合数据中心与电信应用。

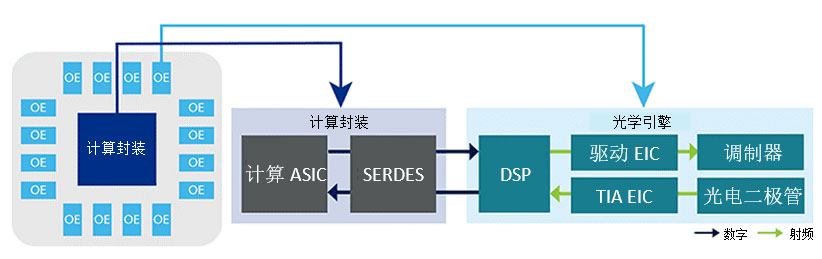

图2:搭载16个光学引擎的共封装光学方案

共封装光学技术将光学收发器(又称“光学引擎”)与HPC器件(如网络交换芯片、GPU或AI加速器)直接集成于单一封装内。该架构以光纤链路取代速率较慢、功耗较高的铜质链路,从而提升带宽密度、能效水平并优化延迟表现。过去一年,英伟达、博通、Marvell、AMD及IBM等行业领军企业均已宣布CPO相关产品的研发进展。

然而,SiPh与CPO的应用也带来了全新的光学测试挑战,亟需通过可扩展的大批量制造解决方案予以攻克。

共封装光学测试的主要挑战

CPO器件的测试涉及多个阶段,首先是光子集成电路的晶圆级测试。这一阶段的核心挑战在于实现亚微米级的光纤对准精度:连接激光器与功率计的光纤,必须以极高精度与晶圆上的光耦合器对准。相比之下,如今大多数电探针台的对准精度仅能达到数十微米级别。这种高精度对准对于确保功率测量的准确性及特定波长的响应性能至关重要。

晶圆分割后,光子集成电路在集成至共封装器件前必须再次进行测试。测试可采用裸片形态开展,也可在完成部分封装后实施。器件可能配备用于无源对准的光学连接器,或需进行有源光纤对准操作。连接器标准的缺失进一步加大了自动化测试的难度,这就要求测试系统支持多种连接器类型。

高速(或称“全速”)测试同样不可或缺。部分器件内置自测试功能,可生成112 Gbps或224 Gbps的PAM4数据。这类测试需要在发射端口与接收端口之间实现光回环;其他器件则需借助外部高速示波器和误码率测试仪验证性能。

最后,当光学引擎与网络ASIC、GPU或AI加速器完成共封装后,需对整个封装进行测试。当前的CPO设计中,计算芯片的2至4个侧面会集成4至36个光学引擎,这就要求自动化测试系统必须满足以下需求:在器件所有侧面建立光学连接,提供高功率激光器,支持任务模式测试所需的光回环功能,同时处理数千瓦的热负载。

迈向大规模量产测试

仅在原型阶段攻克这些挑战远远不够。当前可插拔收发器的年出货量为500万至1000万件,而随着CPO技术的普及,光学引擎的需求量有望攀升至数千万乃至数亿件。人工测试或半定制化测试方案已无法满足如此庞大的量产需求。

为应对这一挑战,需将光学仪器与对准系统集成到数千套自动化半导体测试单元中,且这些单元需与晶圆代工厂及OSAT基础设施实现无缝对接。这类“光电”测试单元必须兼顾易用性,确保操作人员与支持人员均可熟练操作,而非仅面向光学工程师开放。唯有高产能的自动化测试解决方案,才能充分释放SiPh与CPO技术的潜力,助力下一代数据中心实现更低功耗与更高带宽的双重目标。

泰瑞达:引领光学测试创新之路

泰瑞达始终走在技术前沿,针对SiPh与CPO全生命周期的各个测试环节——从晶圆级测试到共封装器件测试,覆盖ATE、SLT及板级测试等多类平台,均研发了对应的测试解决方案。泰瑞达近期推出业内首款硅光子学双面晶圆调试量产方案,简化了电学与光学测试流程。同时,泰瑞达还收购了Quantifi Photonics,将高通道数、高灵活性的光学测试设备纳入自身产品矩阵。凭借深厚的电学测试技术积淀与前沿的光学测试能力,泰瑞达正以“光速”推动硅光子学与共封装光学技术在AI及HPC领域的应用。