半导体生态系统如何应对全球挑战

在法规变化、技术发展和人才流动的大环境下,测试市场的领军企业扮演着举足轻重的角色

半导体产业正经历快速变革。多国政府出台相关政策,支持将半导体产能迁回本土,这使得亚洲、美国和欧洲之间的资源配置呈现出新的格局。与此同时,半导体企业也正争相发展和应用高带宽内存(HBM)和异构集成等新技术。此外,地缘政治因素(例如美国旨在激励本土半导体产业的《CHIPS》法案)、工程师人才短缺,以及人工智能(AI)发展对芯片性能提出的更高要求,既让众多企业面临棘手挑战,同时也加速了行业发展进程。

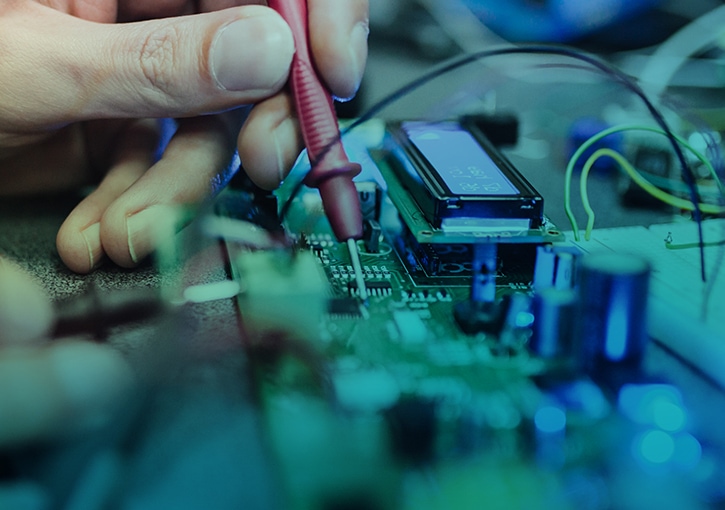

这对半导体测试意味着什么?自动测试设备(ATE)公司不断改进技术,提升自动化水平,并与半导体制造商密切合作,在应对解决这些挑战的过程中发挥关键作用。事实证明,测试资源至关重要,可以保障半导体产业持续创新,并有助于满足日益增长的全球市场需求。

地缘政治和半导体影响

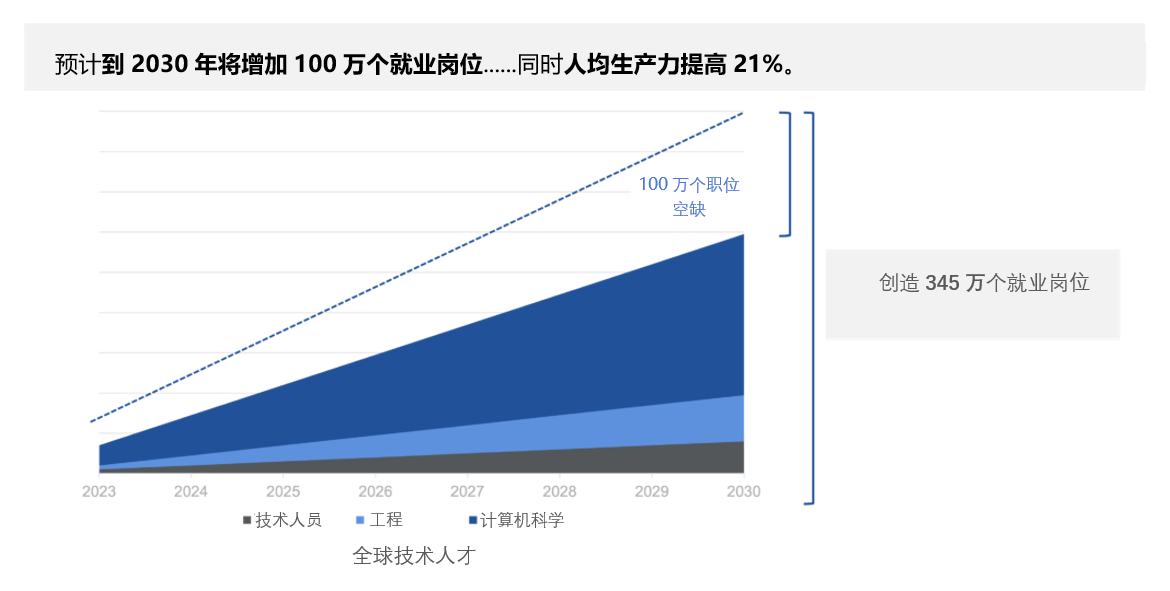

半导体产业格局正在经历重大调整,美国和欧洲政府纷纷出资支持将半导体制造产能迁回本土。美国的《CHIPS》法案旨在增强美国国内的半导体生产和研发实力,是一项影响深远的立法举措。该法案提供了大量资金和一系列激励政策,以应对近年来供应链中断和地缘政治紧张局势所暴露出的脆弱性。同时,资金也将用于培养人才。据估计,未来几年美国半导体行业将面临7万至9万的人才缺口;即便生产效率会不断提升,到2030年,全球半导体产业的职位空缺仍将高达百万以上。

《CHIPS》法案还资助了先进半导体技术研究,从而推动了对创新半导体测试方法和先进测试设备的需求。芯片领域日趋复杂,先进封装和异构集成技术加速发展,测试行业亟需开发更先进的测试方法和设备,进而更好地满足市场对AI和高性能计算的海量需求。

欧洲和亚洲也在积极推行类似的计划,致力于加强自身的基础设施建设。各国家/地区之间的互动关系错综复杂:亚洲(尤其是台湾地区和韩国)仍然掌握着半导体制造领域的主导力量,与此同时,美国和欧洲也正斥巨资构建本土半导体生态系统。

《CHIPS》法案对测试行业影响广泛。随着资本的涌入,半导体产能得到提升,测试设备和服务的需求也随之攀升。美国新建晶圆厂和封装厂陆续投产,美国国内对半导体测试资源的需求也日益增长。

测试行业的新需求与新机遇

目前正值半导体设计、开发和测试发展的关键时期,政府也为此提供了重要的资金支持,以推动基础设施建设。AI的快速发展,使得人们越发重视先进数字芯片的性能和可靠性。在全球范围内,那些要求超快运行速度的应用对此类芯片的需求非常旺盛,而且这些应用的复杂度和功耗也更高。

半导体制程趋向微缩(例如进一步缩小至5nm以下),保障芯片性能、可靠性和能效的难度呈指数级上涨。微型化趋势下的每一次进步,都会给制造精度、热管理和缺陷检测领域带来新的挑战。此外也会给所有晶圆厂设备带来更大的压力,这其中也包括ATE系统。制造商需依靠这些系统来确保最终的芯片良率,进而保障自身的营收表现。

众所周知,仅依靠缩小半导体制程来提升芯片性能的时代已经逐渐远去。为了延续摩尔定律的发展趋势,我们必须在设计、材料和封装等方面进行创新。为了达到所需的处理速度,芯片制造商纷纷采用先进封装技术,包括多个异构集成半导体裸片(芯粒)和2.5D/3D封装结构。这对晶圆厂提出了更高要求,它们必须更可靠地生产合格裸片(KGD)和合格中介层(KGI)。因此,在将裸片组装成更大系统之前,需要使用越来越复杂的测试方法来验证其性能和可靠性。

ATE行业积极应对多种因素交织造成的复杂局面

面对以上种种挑战,泰瑞达始终致力于引领行业发展,确保全球半导体生态系统持续创新并保持繁荣。

为了应对全球半导体产业剧烈变化下的需求,泰瑞达采用了一套灵活的测试策略。其中包括调整制造流程中的测试环节,从而有效管理质量成本。早期测试有助于尽可能减小废品成本;而后期测试则可以确保产品质量得到全面把控。这种平衡式策略能够确保测试操作全流程的质量始终如一,同时充分发挥数据分析的优势,降低成本并提高良率。

深入探讨测试策略的左移和右移

2.5D/3D封装确实有助于延续摩尔定律,但要确保其经济上的可行性,必须在制造初期就着力降低缺陷漏检率(即最终进入成品的缺陷数量),从而降低废料成本。在流程中将测试左移或右移,有助于实现这一目标,尽可能减小总体成本。

左移要求尽早提高测试覆盖率,这发生在晶圆检查和部分封装期间,有助于尽可能早地筛选出KGD,降低后续封装成本。然而,这种做法虽然能够减少废品,但也可能会增加测试成本,因此必须权衡利弊。

右移策略是在流程后期提高测试覆盖率,以发现缺陷并保障质量。这要求终测(或系统级测试)具备更优异的并行处理能力,可以在满足质量目标的同时降低成本。高良率测试可以移至这些后期阶段以优化效率。

我们的目标是在整个制造过程中兼顾质量和良率,从而优化总体成本。我们的策略包括:通过降低晶圆探测环节的缺陷漏检率来降低废品成本,以及高效进行大规模生产测试来降低测试成本。总的来说,我们需要通过动态连续的过程分析,来决定采用左移还是右移策略。利用现有的宝贵数据,我们可以灵活调整整个芯片制造过程的测试策略,形成持续改进的闭环,从而在提高良率的同时,尽可能降低测试成本。

通过灵活的测试策略应对挑战

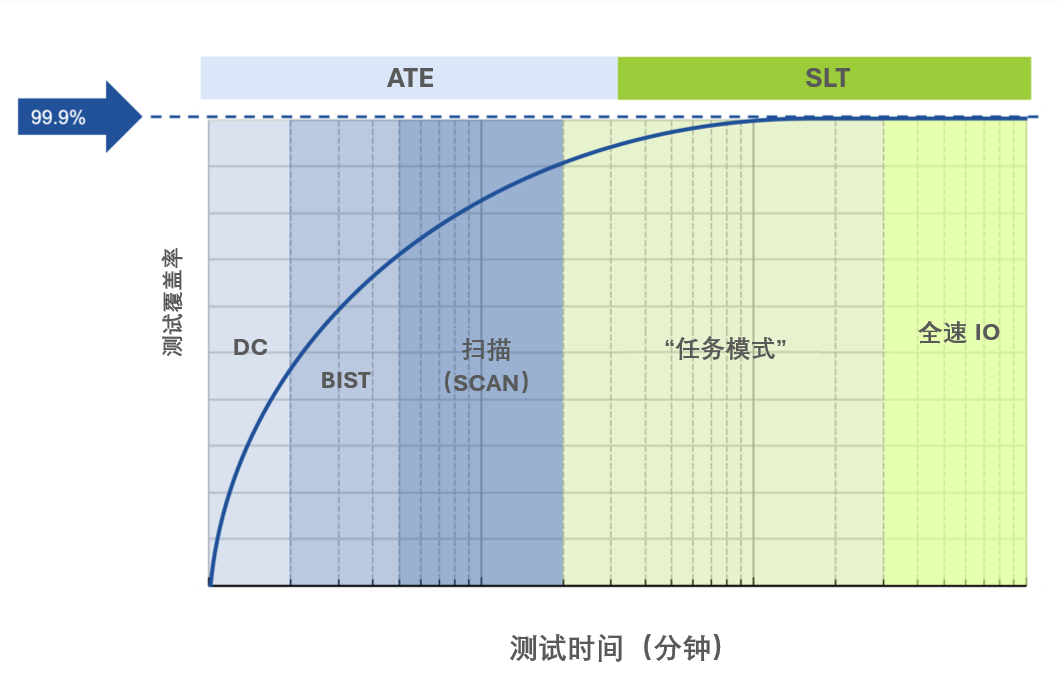

如今的动态测试覆盖还将ATE(如泰瑞达的UltraFLEXplus)与系统级测试(SLT)相结合,后者可以在泰瑞达的Titan平台上进行。SLT通过模拟真实应用环境来优化集成半导体芯片验证。这种测试对于片上系统(SoC)和系统级封装(SiP)等先进技术尤其有用,能够通过数据分析来有效识别故障,控制测试成本,并提高良率。

预集成测试通过高效的KGD和KGI流程来减少缺陷产品,确保最终封装中仅使用功能完好的裸片和中介层。对于3D堆叠IC,则通过先进的3D-DFT测试访问架构进行全面的可靠性和性能测试。

至关重要的是,针对ATE的数据分析,通过提供趋势和异常的解读,帮助制造商在制造过程中实现更好的控制。

AI能够进一步帮助分析这些趋势,优化测试参数并实时主动地进行调整,从而提高良率并降低成本。泰瑞达的Archimedes分析解决方案提供了一个开放式开发环境,支持在边缘设备进行实时分析,用户可以选择开箱即用或定制型解决方案,十分易于部署。

同样,旨在降低数据中心功耗的硅光子技术,也要求开发同步进行的数字和光子测试。为了实现高速数据传输和低功耗,光子技术与电子技术的集成应用日渐普及,测试解决方案也需随之优化,以适应共封装光学器件。

利用数据和自动化打造下一代ATE

展望未来几年,我们可以预见,碳化硅(SiC)和氮化镓(GaN)等新型半导体材料以及集成光子器件的应用会越来越广泛,市场对相关专用测试设备的需求也将日益增长。这将推动提升针对高电压/高电流和低电压/低电流的测试能力,进而有效处理单一封装内的多种不同材料。

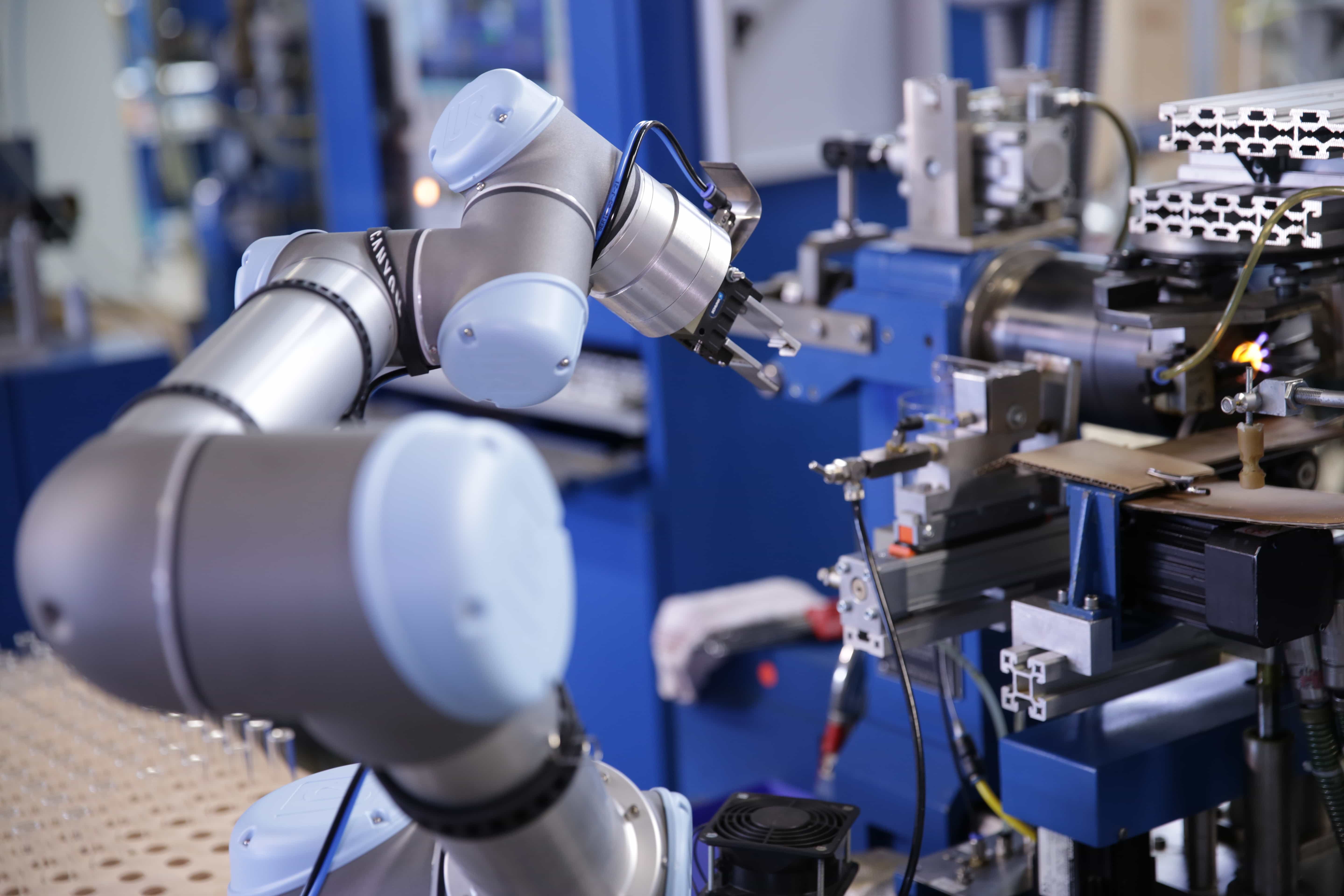

端到端自动化可能会发挥关键作用。通过覆盖晶圆到最终封装的全自动测试流程,可以大幅减少人为干预和错误。ATE将继续利用AI和机器学习来提高测试精度,预测元器件故障,并实时优化测试参数。

AI驱动的数据分析将有助于识别模式和趋势,从而主动控制质量,并提高良率。泰瑞达通过“SEMI智能数据-人工智能倡议”支持业界引入更多AI技术。这是一个出色的平台,将大力推动利用半导体生态系统中的数据和人工智能创造价值。作为该倡议的成员,泰瑞达正致力于推动测试数据输出的标准化发展,以促进业界合作,缓解IP泄露和供应商锁定等担忧。

显而易见,人工智能、先进半导体技术和地缘政治动态的相互作用,正在深刻影响着半导体行业的未来。泰瑞达致力于通过灵活创新、开放协作的测试策略,保障半导体产品的可靠性和高质量,充分激发人工智能技术的潜力,创造更美好的未来。