芯粒的行业标准及其在测试中的作用

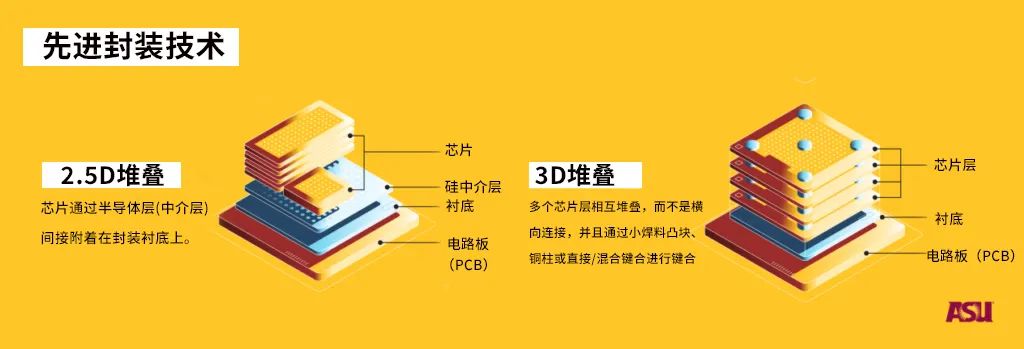

随着半导体行业日渐朝着芯粒、2.5D/3D 封装以及异构集成方向迈进,测试领域正面临着全新且严峻的挑战。以泰瑞达为代表的行业领军者,虽然掌握了应对挑战、驱动创新的关键技术,但要确保整个行业的健康发展,仍离不开高效的协作。而实现高效协作的关键,在于推行标准化。

来源:Arizona State University

在测试生态系统的多个领域中,“标准”发挥着重要作用,不仅促进了高效协作,更激发了创新,还提升了测试效率。从整体上看,这些标准都与集成电路(IC)和半导体芯片的测试及通信协议有关,目的是确保它们在先进系统中能够相互操作、传输数据并可靠运行。

相关标准包括:

- PCIe(高速串行计算机扩展总线):连接计算机组件的高速通信标准

- MIPI(移动行业处理器接口):移动设备使用的高速通信标准

- UCIe(通用芯粒高速互连):专注于在异构系统的芯粒和2.5D/3D封装之间实现高效互连。

- IEEE 1838:制定了3D IC测试标准,特别针对具有硅通孔(TSV)的芯片。

- JTAG1、1149.6及J2C版本:用于测试和诊断IC内互连的边界扫描标准

- SPI(串行外设接口):用于连接微控制器和外设的常见通信协议。

总的来说,这些标准确保了半导体芯片在高度互连的生态系统中无缝的功能性、可制造性和可扩展性。请继续阅读泰瑞达Jeorge Hurtarte的文章,了解这些关键标准、它们对测试的影响,以及泰瑞达对统一测试生态系统的愿景。

通过标准接口测试高性能芯片

行业标准在保障半导体测试的有效性方面发挥着举足轻重的作用,通过确立统一的评估方法,来衡量半导体器件的功能、性能以及可靠性。这些标准有助于解决因半导体设计日益复杂、先进封装技术不断涌现以及异构组件集成所带来的重重挑战。

首先,市场上存在着用于连接GPU和CPU等高性能计算芯片的标准接口,无论这些芯片是采用常规封装还是基于芯粒架构。这些接口大多为串行接口,例如PCIe和MIPI。

这些串行端口通过扫描测试,对芯片内部的数字部分进行检测。测试过程虽然采用的是串行接口,但数据传输模式会被转换为更接近并行的方式。通过连接至芯片内置的“链”,能够同时测试芯片内的所有晶体管。扫描会占用测试设备的大量内存,而对内存的需求越来越大,是行业的普遍趋势。

扫描测试也有不同的类型,其中包括由Synopsys或Siemens等EDA公司推动研发的测试。泰瑞达早在前期便与这些公司展开合作,深入了解其EDA工具在这类扫描测试中所具备的功能特性,以便规划前瞻性布局,确保自身在测试与工具集成方面能够占据有利地位。

Siemens等领军企业正积极推动将监控器直接安装于芯片之上。监控器是微型计算器件,能够监控芯片内特定模块的状态,并提供计算、可靠性和潜在故障等方面的健康状况数据。标准化串行接口和片上监视器的结合,对于支持ATE应对现代芯片的超高复杂度至关重要。

针对芯粒的专门标准有哪些?

对于新兴的芯粒技术,最广为人知的标准或许是专注于裸片或芯粒互连的UCIe。UCIe芯粒互连距离达到毫米级,这带来了可测试性问题。这可能意味着测试设备对静电放电(ESD)探针变得更加敏感,而泰瑞达早就推出了相关解决方案。

对于封装前和封装后测试,应采用IEEE 1838“3D堆叠集成电路测试访问架构标准”。IEEE 1838是3D IC的DfT(可测试性设计)标准。DfT描述如何构建一个能够分别测试多个堆叠裸片的架构,这些裸片可能包含嵌入式核心和3D互连。

中介层测试主要通过点对点连通性探测来完成。合格中介层(KGI)对于确保先进封装达成足够良率至关重要。

对于封装后组装,IEEE P1838定义的主次TAP端口可用来测试裸片间测试访问和互连性能完整性。

更多标准及其对测试的影响

新兴标准包括JTAG 1149.1或1149.6、SPI及J2C(JTAG至CPU)。无论在设计还是制造阶段,这些标准对于确保集成电路(IC)的有效通信、调试和验证都发挥着重要作用。

JTAG 1149.1(又称为IEEE标准1149.1)主要用于边界扫描测试,能够在无需物理测试探针的情况下,对PCB上的各个组件进行测试。该标准提供了一种访问和测试IC内部信号的方法,从而能够有效地检测开路、短路以及互连问题等故障。JTAG支持在制造后对芯片和电路板进行测试,这对于调试和验证电路行为正确性至关重要。

JTAG 1149.6扩展了1149.1标准,以支持现代IC中越来越常见的高速差分信号(如LVDS、USB和高速串行接口)的测试。该标准可用于测试这些高速接口的完整性,确保其正常运行,尤其适用于传统边界扫描技术无法充分测试信号质量和传输情况的系统。

J2C起源于JTAG,主要用于直接连接到CPU或SoC进行测试、调试和编程。J2C支持为了测试而访问CPU的内部状态、寄存器和内存。这在半导体测试领域至关重要,对于复杂处理器开发过程中的调试,以及验证CPU或SoC在制造后是否按预期运行都有着不可替代的作用。

在半导体测试环境中,SPI是一种串行通信协议,常用于与芯片或电路板上的嵌入式元器件或存储器件进行通信。测试设备通过SPI与IC接口,执行功能验证、数据传输测试和存储器编程。

这些标准提供了测试设备和待测芯片(DUT)之间的访问、控制、通信路径,在半导体测试中意义重大。通过这些方法可以实现故障检测,识别短路、开路或信号完整性等问题。它们通过读取和写入测试向量来确保芯片正确运行,并通过帮助工程师在设计和制造阶段查明并解决问题,从而有力地推动了调试和验证工作的开展。此外还可以与其他测试系统共享实时数据,从而进一步提高测试效率。

数据标准提高效率

半导体测试会产生大量数据,倘若能够将这些数据实时地与数据分析平台以及其他下游系统进行共享,将能大大提升效率和产品良率。

然而,不同公司的数据格式可能不兼容。为了解决这一问题,SEMI提出了“智能数据和AI倡议”,旨在为晶圆厂内不同功能之间的数据共享搭建起一个统一的框架。

SEMI智能数据-AI倡议全球负责人兼战略技术顾问Pushkar Apte博士表示:“SEMI的智能数据和AI倡议旨在将数据分析、机器学习、AI和数字孪生技术应用到半导体生产流程中,推动整个生态系统协作发展。随着半导体器件以及用于测试其性能、可靠性和整体质量的ATE系统变得愈发复杂,这种共享的洞察力对于加快创新步伐非常关键。”

作为这一倡议的成员,泰瑞达公司正致力于实现测试数据输出标准化,以鼓励各方之间的合作,避免IP暴露或供应商锁定的风险。泰瑞达设计了Archimedes分析解决方案,这是一个开放的开发环境,能够支持不依赖于特定供应商的分析策略。

Archimedes支持实时访问测试数据,从而可以助力开发者提升分析效率,加快决策。通过对标准化数据框架的支持,泰瑞达公司正助力打造更具协作性和创新性的半导体生态系统。

标准、协作和测试集成

在AI、异构集成和芯粒技术广泛应用的时代,一系列标准为高效、精准地测试复杂半导体系统提供了保障,使得高质量的产品能够顺利走向市场。

随着半导体行业的不断发展,泰瑞达始终走在行业前列,积极制定和实施塑造未来测试技术格局的标准。从UCIe和IEEE 1838等芯粒相关的标准,到通过“智能数据和AI倡议”提出的数据标准,泰瑞达的贡献为打造基于实时测试数据访问的更高效、更可靠且更具协作性的半导体测试流程铺平了道路。展望未来,泰瑞达将继续在定义和推动下一代半导体技术的标准方面发挥关键作用。

Jeorge S. Hurtarte博士目前是泰瑞达半导体测试部门的产品营销高级总监。Jeorge曾在泰瑞达、Lam Research、LitePoint、TranSwitch和Rockwell Semiconductors担任过多种技术、管理和高管职位。他是IEEE 802.11 Wi-Fi标准委员会的投票成员,并是IEEE 802.11ay任务组的秘书。Jeorge目前是IEEE异构集成路线图(HIR)测试工作组的联合主席,同时也是美国加州大学圣克鲁斯分校和菲尼克斯大学的客座教授。