AI推动算力升级,测试护航先进封装与芯粒发展

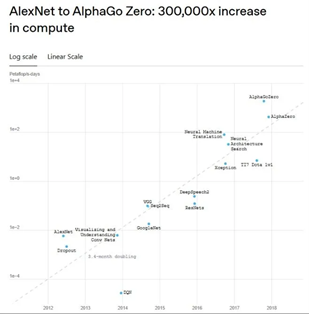

人工智能(AI)正深刻改变各行各业,不仅优化了我们的日常生活体验,而且提升了我们的工作效率和决策能力。然而,AI对算力的需求正以惊人的速度攀升,几乎每三个月就要翻一番(见图1)。为了支撑这一发展势头,半导体行业正突破传统芯片开发模式,进入了以先进集成封装为基础的异构芯粒时代。

(图1:算力需求的增长。 来源:https://openai.com/index/ai-and-compute/)

芯粒的崛起

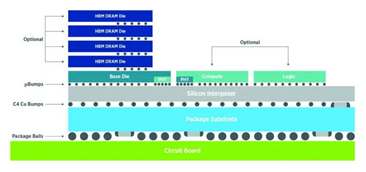

NVIDIA和AMD等芯片公司打破常规,设计出将多个CPU和GPU及高带宽内存(HBM)集成到单个先进封装中的架构。AI的应用场景需要快速访问海量数据,而集成HBM可以满足这一需求。为了将两个、四个或更多的xPU与HBM进行集成,需要采用由台积电开发的CoWos®(Chip-on-Wafer-on-Substrate)先进封装技术,即业内通常所称的2.5D/3D封装(见图2)。此类封装的尺寸可能超过100mm x 100mm,显著大于传统封装规格。因此,测试环节需要使用既能处理大型CoW模组/叠层、又能应对显著提高的散热需求的晶圆中介层探针台。具体要求将在下文讨论。

(图2:2.5D/3D封装架构,来源:泰瑞达)

(图2:2.5D/3D封装架构,来源:泰瑞达)

为了保持最佳性能,此类异构集成的先进封装芯片使用专有高速接口实现高效的数据传输。上述种种需求叠加到一起,使得半导体产业格局日趋复杂。

测试的复杂性随芯片技术的进步而不断加剧

随着封装复杂度的提升,测试策略也必须更加周密。在从单片裸片向芯粒架构过渡的过程中,由于测试IP现在分布于多个裸片,某些情况下甚至分属不同的设计团队或公司,因此长期沿用的测试方法已无法直接照搬。这种碎片化趋势要求业界更清晰地定义每个阶段(裸片、桥接结构、中介层、衬底和叠层)所要测试的内容,并明确每个范围适用的标准或技术。

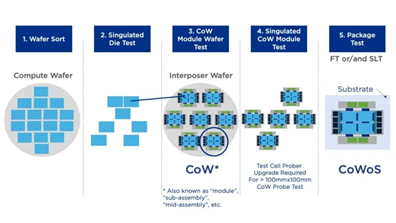

将多个裸片封装到单个基于芯粒的系统中是一项重大进步,但这也带来了一个关键挑战:在最终组装之前,必须验证每个组件是否正常工作。多裸片封装对筛选流程提出了更高要求。为了避免良率下降,仅确认裸片合格已不再足够。中介层、衬底、桥接结构和叠层等各个层级,也需要采用相应的测试技术进行验证。因此,行业正步入“全项合格”的验证模式,以实现从“合格裸片”(KGD)到“合格中介层”(KGI)、“合格CoW”(KG-CoW)等的全面验证。(图3)

(图3:为确保KGD和KG-CoW而可能采用的测试节点。来源:泰瑞达)

(图3:为确保KGD和KG-CoW而可能采用的测试节点。来源:泰瑞达)

芯粒间的高速通信带来了额外的复杂性。以GPU与HBM之间的数据传输为例,必须以极快的速度交换数据。然而,芯粒数据接口的物理和电气指标因制造商而异。虽然通用芯粒高速互连(UCIe™)等开放标准正在持续演进,但芯粒接口仍然存在显著差异。为了适应这种多样性,测试解决方案越来越需要能够像芯片原生协议一样运行的接口IP,以避免电气过应力风险或探针引起的相关的损伤。目前已有部分供应商能够提供符合UCIe标准的PHY和控制器IP,供芯片厂商集成使用,从而让自动测试设备(ATE)平台能够安全且一致地测试高速链路。

(图4:芯片级裸散热,来源:泰瑞达)

(图4:芯片级裸散热,来源:泰瑞达)

厂商和测试操作人员还必须密切关注热管理。算力的提升不可避免地会加大散热需求压力,迫使业界采用更先进的散热方案,甚至可能在封装内部实施液冷(见图4)。封装内裸片越多,意味着测试机需要的资源也更多。更多晶体管则意味着更高的电源电流需求、更多的电源仪表和更严峻的热挑战。为此,业界必须采用创新的散热方案,并实施先进的自适应热控制(ATC)策略。

此外,制造环节的测试必须考虑中介层,而中介层是指将芯片与衬底或其他有源组件进行电气连接的物理接口层。例如,在多层或2.5D封装中,多个裸片放置在中介层上,而中介层装配在衬底之上。中介层起到微型硅电路板的作用,在上下层之间传输信号。为确保先进封装达到预期良率,中介层也必须是合格裸片或合格中介层(KGI)。

泰瑞达解决方案

随着芯片演进,半导体元件数量不断增加,测试复杂度也同步提高。而测试复杂度的提升导致对扫描测试向量内存的需求越来越大。为了满足这一需求,泰瑞达增加了扫描向量内存容量,确保即便最复杂的半导体设计也能得到有效测试。

泰瑞达最先进的ATE平台UltraFLEXplus能够提升芯片测试的产能。凭借泰瑞达独特的Broadside芯片接口板(DIB)设计架构,UltraFLEXplus优化了信号布线,从而在减少DIB PCB层数的同时,实现更好的信号性能。Broadside融合了两项关键技术:其一为泰瑞达的PACE架构,通过在测试机内嵌入控制器来提升产能;其二是对测试结果的处理任务进行合理分工,从而提高处理效率。

顺应此类先进芯片日益集成光学接口的趋势,泰瑞达也在UltraFLEXplus平台中整合了先进的光学测试能力。这款率先推出的双面晶圆解决方案,可为新兴的硅光子芯片与共封装光学应用提供量产测试支持,满足电气与光学测试同步进行的需求。

此外,泰瑞达与诸多领先的生态供应商持续合作,以满足大规模异构集成先进封装芯片严苛的先进自适应热控制测试要求,助力实现从“合格裸片”到“合格CoW”乃至更高层级的验证目标。

AI和芯片测试的未来

业界越来越清晰地认识到,芯片测试已成为当今芯粒和先进封装发展趋势中不可或缺的一环。随着这一趋势的推进,AI算力将继续以前所未有的速度演进,而芯片测试将在保障芯片质量方面发挥关键作用,确保高质量芯片能够在当今市场所要求的更短周期内顺利交付。芯片测试虽很少被聚光灯照耀,却始终是AI发展背后的重要基石,稳步推动下一波技术突破。