优化自动测试设备(ATE):提升质量并应对复杂度挑战

原文转发自“EE Times”。

AI正在改变世界,推动前所未有的增长与创新。高性能芯片作为这场变革的核心,其复杂度持续攀升、精度要求日益提高,先进技术集成度也不断提升。

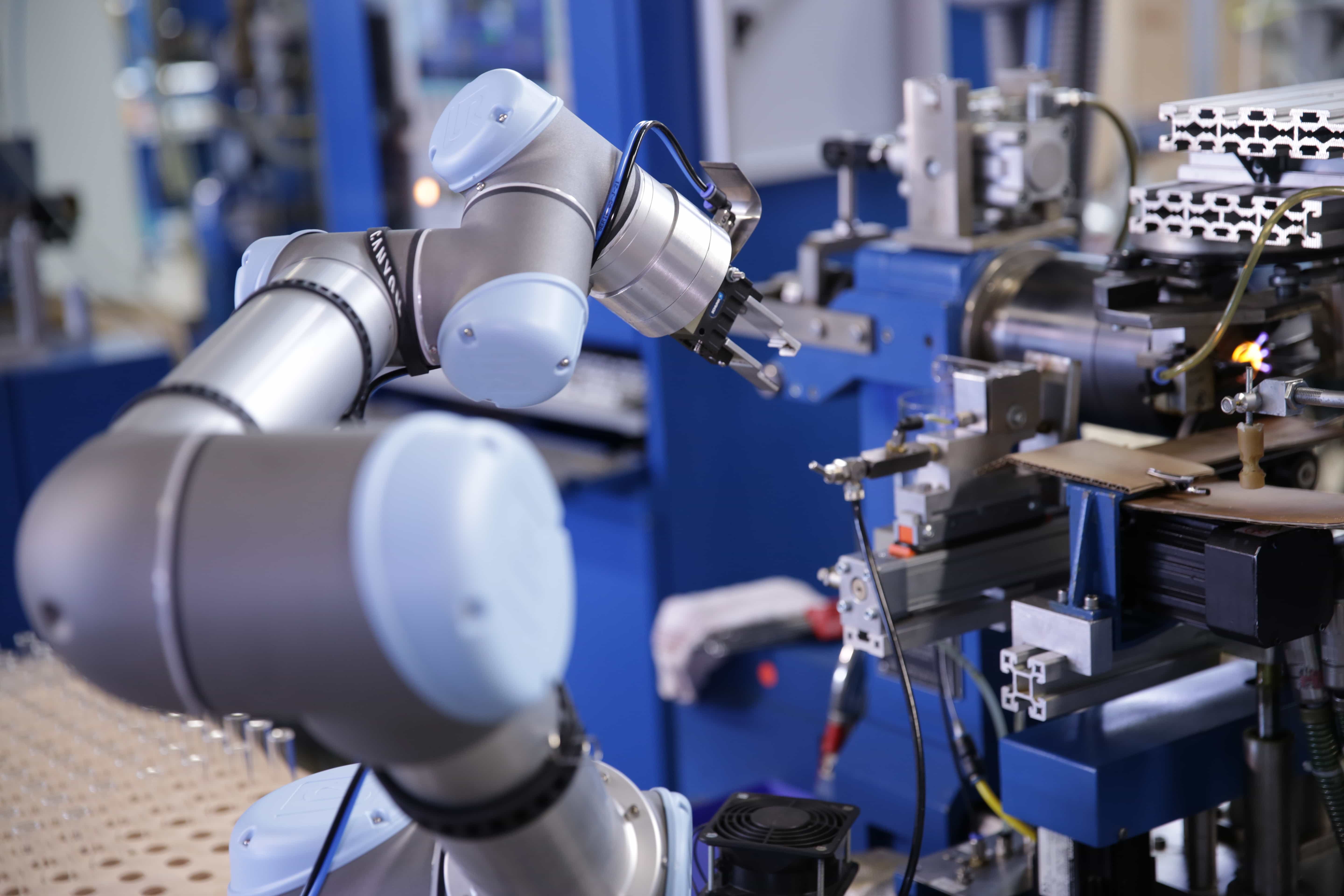

这种迅猛变革对半导体制造依赖的数字技术和自动测试系统提出了新要求。这一全面转型需要灵活的测试策略,以应对新工艺架构、异构封装和软硬件集成复杂性等挑战。

当今半导体测试行业正以多维度策略应对这些挑战。自动测试设备(ATE)行业通过升级测试设备、集成AI技术、采用新标准并优化测试流程,确保紧跟半导体技术快速发展步伐并满足制造商需求。

多种因素叠加导致复杂度持续攀升

数十年来,数字制程微缩技术推动芯片数字性能和晶体管密度呈指数级增长。尽管晶圆制程微缩在一些方面(主要是成本和功耗)的效益趋缓,但先进节点仍持续向5 nm以下几何尺寸演进,每代半导体都会增加数以百万计的晶体管,需要测试和验证。

与此同时,半导体行业正转向多裸片(又称芯粒)异构集成的先进封装技术。该技术允许制造商在单个封装内整合CPU、GPU、AI加速器和高带宽内存等不同处理单元,针对特定应用优化性能。芯粒和2.5D/3D封装等先进封装技术突破单片设计局限,实现更高的性能、效率和灵活性。

此外,异构集成加剧测试复杂度,需要高精度测试策略。例如,必须开发专用探针和接口,确保每个芯粒及其集成系统的功能、可靠性和性能均达标。

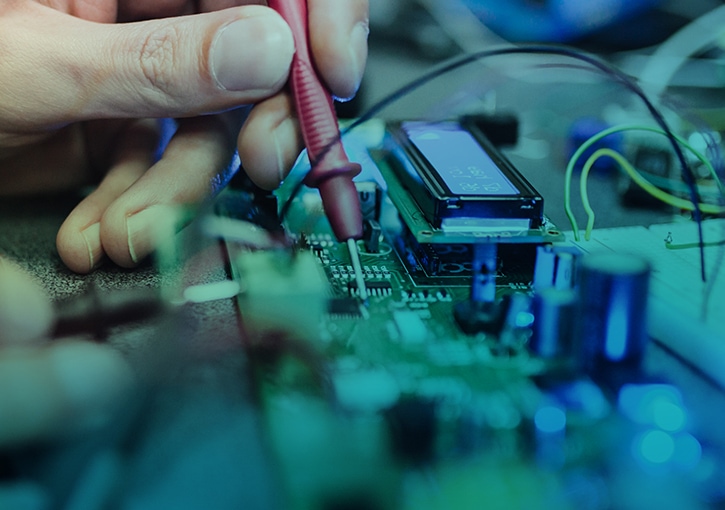

测试半导体芯片

AI和高性能计算(HPC)的快速演进,推动晶体管规模和封装密度持续提升。5G、Wi-Fi 6和Wi-Fi 7等技术催生对更快数据传输速率和更高带宽解决方案的需求,其实时数据传输能力成为工业和商业自动化的核心。

这些因素共同推高市场对ATE的需求以及对半导体测试伙伴的依赖。随着2 nm等更先进制程节点的成功导入,工程技术能力和配套工具(包括通过良率学习和峰值生产来减少误差的ATE)面临更大压力。

利用灵活的测试策略优化良率、测试成本和质量

灵活的测试策略应随需求演进,以应对新工艺节点、基于芯粒的架构及其他新兴技术带来的挑战。

- ATE与系统级测试相辅相成

动态测试覆盖将ATE和系统级测试(SLT)衔接,后者是一种在模拟最终使用环境的条件下评估半导体芯片的测试方法。

这种结合可更全面验证待测芯片的功能及其与软件和其他硬件的交互性能,尤其适用于SoC和系统级封装(SIP)等先进半导体技术,因为其实际交互和软件集成至关重要。通过该方式,可有效识别故障,妥善平衡成本,制造商还可借助数据分析提高良率。

- 预集成和综合测试方案

确保最终封装中仅集成功能正常的裸片和中介层至关重要。严格的预集成测试(“合格裸片”和“合格中介层”流程)能够验证每个元器件的功能,降低出现缺陷的可能性。针对3D堆叠IC的全面测试访问需求,全堆叠范围的3D-DFT测试访问架构支持对可靠性和性能进行有效测试。

- 考虑新兴技术和测试需求

为解决数据中心的能耗问题,业界开始引入硅光子等新技术。然而,该技术需要同步开展数字与光子测试,业界目前仍在研发这一技术能力。随着光子与电子技术日益融合,业界需要优化适配共封装光学器件的光子测试设备,以满足数据中心和HPC应用对高数据传输速率和低功耗的核心需求。

- 利用数据分析和AI集成

理想情况下,测试合作伙伴可通过ATE的数据分析能力为制造流程提供反馈和控制。这些数据有助于识别趋势和异常,以便企业能够进行前瞻性调整,从而提高良率并降低成本。

AI可以帮助分析趋势、优化测试参数并做出实时决策,以提升测试效率。这种集成要求半导体生命周期的各阶段之间实现安全数据共享,而这在分散的无晶圆厂模式中极具挑战性。

例如,芯片从晶圆到封装、再到SLT的过程中,ATE行业必须确定筛查故障机制的最佳测试点。此类决策虽基于特定芯片的制造工艺成熟度,并由人工做出,但关键依赖动态测试覆盖,通过ATE和SLT系统之间的通信链路确定检测和处理故障的位置。AI算法的集成可进一步改善此过程,通过管理测试中产生的海量数据,确保测试兼具高质量与成本效益。

- 平衡测试覆盖率以优化良率、成本和质量

为实现灵活的测试流程,需要结合使用“左移”和“右移”策略,以优化整体质量成本,并平衡早期与后期测试阶段的权衡。通过数据分析确定半导体制造过程中的最优测试点。

早期测试有助于尽可能减小废品成本,而后期测试则可以确保产品质量得到全面把控。这种整体方法能够优化整个测试生态系统,提升良率、降低成本并维持高品质。

推动行业增长和塑造行业格局

AI应用已对测试市场产生深远影响,而ATE行业仍处于未来数年增长趋势的起步阶段。AI作为变革性长期增长引擎,其影响力已渗透至网络领域以及高级驾驶辅助系统(ADAS)等边缘AI应用。

展望未来,半导体测试市场中计算类细分市场规模增速将超预期,2024年总体可触达市场(TAM)预计达到16亿美元。

如今,AI带来的行业增长集中于云端AI能力建设,尤其是基于海量数据集的大型语言模型(LLM)训练。LLM需要通过云端和边缘推理应用解决实际问题,方能释放商业价值。而半导体测试凭借工具、数据和协作,成为保障数字系统及芯片质量和可靠性的核心环节。

LLM训练的硬件要求极高,涵盖通用细粒度计算、高带宽内存、密集网络互连及海量电力供应,所有这些都需要创新的测试策略来确保质量和可靠性。

AI时代与半导体测试

AI时代为先进封装领域的异构集成带来了新的机遇。此类发展与先进制程节点、新互连标准等新兴技术相结合,正对EDA到量产流程及优化工作产生巨大压力。

为应对这些挑战,需要创新的测试策略、先进的设备以及软硬件集成能力,以确保当今复杂半导体的可靠性和性能符合要求。灵活全面的半导体测试策略是优化良率、测试成本和质量的关键。

测试合作伙伴应提供动态测试覆盖和全制造流程平衡测试,关注新兴技术,通过数据分析实现持续改进,并将AI集成到测试过程中。这些因素是保障AI时代半导体芯片具备高质量和高可靠性的关键。

与测试伙伴协作有助于实施全面的解决方案:搭建稳健的测试网络,通过有效检测故障优化质量成本,平衡成本,以及借助数据分析提升良率。