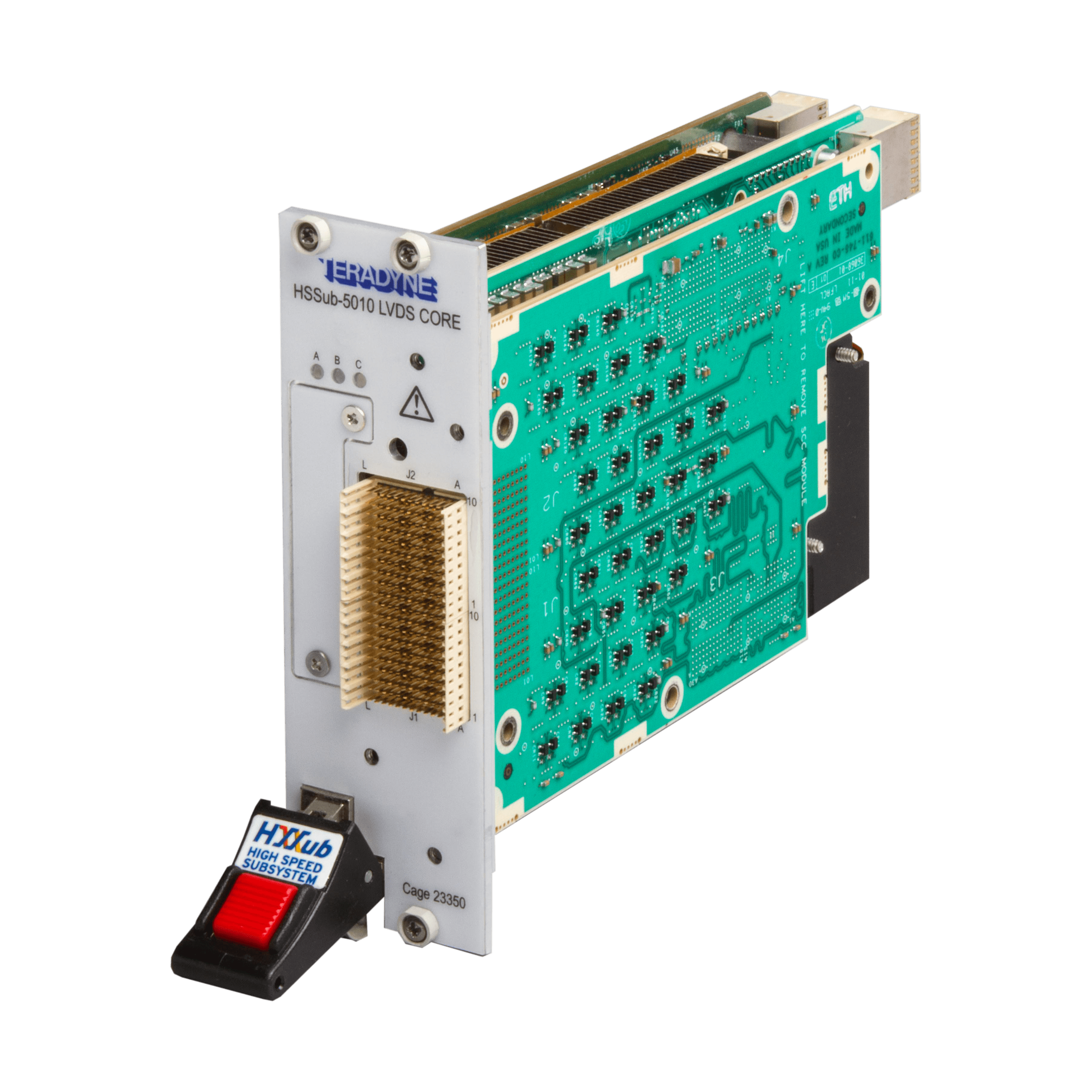

HSSub-5010

LVDS Core Instrument

Configurable LVDS Bus Capability with Integrated Real-Time Processing

Best choice when current or future requirements include:

- Custom and standard parallel bus implementations with up to 72 LVDS pairs and data rates to 800Mb/s

- FPGA and processor configurability to support a wide range of lower and upper level protocols

- High bandwidth, memory, and processing capacity coupled with predictable low latency interactions

- Multiple concurrently operating buses

- predictable low latency interactions

- Wired or optical I/O support

- Ideal for addressing legacy or new designs, as well as replacing obsolete or inadequate LVDS instrumentation

- Combines low-level Tier 1 (I/O Bus Processing) and upper-level Tier 2 (Real-Time Computing) capabilities of the HSSub Three Tier Architecture in a single instrument

- Reconfigurable Tier 1 implemented by a large Test Defined FPGA and Tier 2 by a dedicated processor and real-time operating system (RTOS)

- Configured in seconds by HSSub Apps

- HSSub Apps employ the HSSub TriFlex Infrastructure Software to provide application-specific instrument configurations

- High-level TPS access on the Windows computer

- Totally open access to the Test Defined FPGA and programs on the RT processor

- HSSub App development, if required, is simplified by FPGA template code based on standard design patterns

- HSSub Apps developed by Teradyne, end users, and third-parties